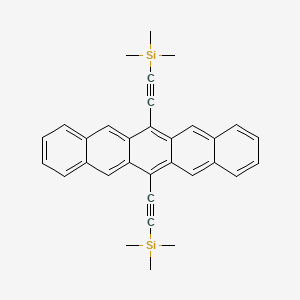

TES pentacene

Content Navigation

CAS Number

Product Name

IUPAC Name

Molecular Formula

Molecular Weight

InChI

InChI Key

SMILES

solubility

triethylsilylethynyl pentacene synthesis

Synthetic Strategy and Pathway

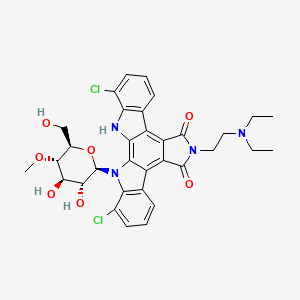

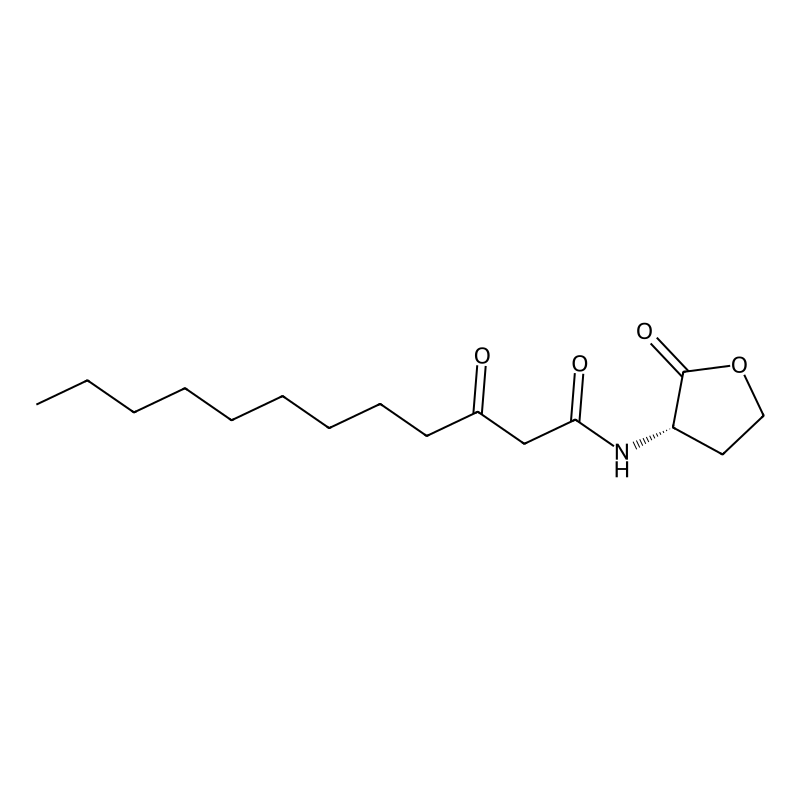

The synthesis of silylethynyl-substituted pentacenes like 6,13-bis(triethylsilylethynyl)pentacene (TES-Pn) generally follows a multi-step procedure. The core strategy involves a key cross-coupling reaction between a pentacenequinone derivative and a silylacetylene reagent [1] [2].

The following diagram illustrates the logical workflow and major steps involved in this synthesis:

Key Properties and Characterization Data

The table below summarizes the properties of TES-Pentacene in comparison to its close relative, TIPS-Pentacene, as identified in the search results.

| Property | 6,13-Bis(triethylsilylethynyl)pentacene (TES-Pn) | 6,13-Bis(triisopropylsilylethynyl)pentacene (TIPS-Pn) |

|---|---|---|

| Solid-State Packing | One-dimensional (1D) π-stacking [3] | Two-dimensional (2D) "brickwork" arrangement [3] [4] |

| Optoelectronic Anisotropy | High (Anisotropy ratio ~21-47) [3] | Moderate (Anisotropy ratio ~3-10) [3] |

| Key Structural Feature | Strong intermolecular transition dipole along the core stacking axis [3] | 2D packing structure [3] |

Experimental Considerations and Notes

- Aromatization Step: The final, crucial step to obtain the conductive pentacene core involves a reduction (deoxygenation) of the intermediate. Common reagents for this include tin chloride (SnCl₂) or other chemical reducing agents [2].

- Molecular Orbital Tuning: A 2025 study highlights a related strategy using N,N'-diethynylated 6,13-dihydro-6,13-diazapentacene. This approach tunes frontier molecular orbitals while maintaining the parent pentacene's geometry and π-stacking, significantly enhancing hole mobility in field-effect transistors [4]. This represents an advanced direction in the field.

References

- 1. Excited-State Dynamics of 5,14- vs 6,13-Bis ... [pmc.ncbi.nlm.nih.gov]

- 2. Process for preparing substituted pentacenes [patents.google.com]

- 3. impact of structural anisotropy on optoelectronic properties [pubmed.ncbi.nlm.nih.gov]

- 4. Molecular Orbital Tuning of Pentacene-Based Organic ... [pmc.ncbi.nlm.nih.gov]

Electronic Properties of Pentacene and Selected Derivatives

The following table summarizes the available experimental data on the lowest excited singlet (S₁) and triplet (T₁) state energies for pentacene and related molecules, which are crucial for applications like singlet fission [1] [2].

| Molecule | S₁ Energy (eV) | T₁ Energy (eV) | Remarks / Context |

|---|---|---|---|

| Pentacene (PEN) | ~1.83 [1] | ~0.86 [1] | Values from benchmark set; key for singlet fission studies. |

| 6,13-diazapentacene (6,13-DAP) | Information Not Available | Information Not Available | Discussed in comparative studies; specific energy values not provided in search results [2]. |

| 6,7,12,13-tetraazapentacene (TAP) | 1.6 [2] | 1.2 [2] | Adsorbed on Au(111) substrate; optical gap assigned to S₀→S₁ transition [2]. |

Experimental & Computational Methodologies

The research into these electronic properties relies on advanced spectroscopic and computational techniques.

- High-Resolution Electron Energy Loss Spectroscopy (HREELS): This experimental technique was used to assign the energies of the lowest excited singlet and triplet states (S₁ and T₁) for molecules like TAP on a gold substrate. This method involves probing the vibrational and electronic structure of surfaces and adsorbed layers [2].

- Screened Range-Separated Hybrid Functional within a Polarizable Continuum Model (SRSH-PCM): This is a state-of-the-art computational approach based on Time-Dependent Density Functional Theory (TD-DFT). It is benchmarked to accurately predict the S₁, T₁, and T₂ (second triplet) state energies of organic semiconductors in a condensed phase. The method successfully incorporates the effect of the electrostatic environment (e.g., a crystal or solvent) on the excited state energies, achieving an average error of 0.11 eV for S₁ and 0.06 eV for triplet states [1].

The diagram below illustrates the general workflow for determining excited state energies using the computational SRSH-PCM method.

Workflow for calculating excited state energies using the SRSH-PCM method [1].

Key Context for TES-Pentacene

While direct data on TES-pentacene is unavailable in the current search, here is some contextual information:

- Molecular Structure: TES-pentacene is a derivative where triethylsilylethynyl groups are attached to the pentacene core, specifically designed to enhance stability and solubility [3].

- Research Focus: Much of the current research on pentacene derivatives, including studies on nitrogen-substituted variants like TAP, focuses on how these structural modifications alter the electronic structure and excited state energies, which is directly relevant to understanding TES-pentacene [2].

References

Core Chemical Identity

The table below summarizes the fundamental chemical and physical properties of TES pentacene.

| Property | Description |

|---|---|

| Chemical Name | 6,13-Bis((triethylsilyl)ethynyl)pentacene [1] |

| CAS Number | 398128-81-9 [1] |

| Molecular Formula | C₃₈H₄₂Si₂ [1] |

| Molecular Weight | 554.91 g/mol [1] |

| Melting Point | 261-266 °C [1] |

| Form | Crystals [1] |

| Semiconductor Type | P-type [1] |

Synthesis and Experimental Protocols

Synthesis of this compound

The synthesis follows a well-established route for creating ethynyl-substituted pentacenes [2]. The general workflow is as follows:

Synthesis workflow for this compound, involving addition to pentacenequinone followed by reductive aromatization.

- Addition Reaction: Commercially available pentacenequinone reacts with the anion of triethylsilylacetylene in a Grignard-type or similar reaction. This step adds the substituted alkyne groups and forms a diol intermediate [2].

- Reductive Aromatization: The diol intermediate is converted into the final aromatic this compound molecule. This can be achieved using reagents like tin(II) chloride (SnCl₂), hydroiodic acid (HI), or a milder mixture of potassium iodide (KI) and sodium hypophosphite (NaH₂PO₂) in acetic acid. The purity of the starting materials is critical for achieving high-performance electronic material [2].

Thin-Film Deposition for Device Fabrication

Unlike unsubstituted pentacene, this compound can be processed from a solution, enabling lower-cost fabrication methods [3]. The following protocols are commonly used:

- Solution Casting & Spin Coating: A solution of this compound in a suitable organic solvent (e.g., toluene, chloroform) is prepared. The solution is then deposited onto a substrate either by drop-casting or spin-coating. Slow solvent evaporation is crucial for allowing the molecules to self-organize into large, highly ordered crystalline domains, which is essential for good charge transport [2].

- Inkjet Printing: This technique allows for precise patterning of the semiconductor. It requires formulating a stable ink with optimized viscosity and surface tension, often using a blend of solvents. The printed film then crystallizes as the solvent evaporates [2].

Material Properties and Device Performance

Crystal Packing and Morphology

The bulky triethylsilyl groups dramatically alter how the pentacene molecules pack in the solid state compared to the parent pentacene. This compound typically forms one-dimensional "slipped-stack" or columnar structures [2]. This is a key differentiator from the similar TIPS pentacene derivative, which forms two-dimensional brickwork π-stacked structures. This difference in packing leads to significant variations in thin-film morphology and electronic performance [2].

Electronic Properties and OFET Performance

In organic field-effect transistors (OFETs), the performance is highly dependent on film morphology [2].

Relationship between molecular packing, film morphology, and device performance for different silylethyne-substituted pentacenes.

Due to its specific crystal packing, this compound tends to form thin, needle-like crystals in thin films that do not cover the substrate uniformly, leading to poor inter-grain connectivity and, consequently, very low hole mobility in the order of 10⁻⁵ cm²/V·s in bottom-contact OFETs [1] [2]. In contrast, optical studies on single crystals suggest the intrinsic material potential is much higher, highlighting the critical role of film morphology [2].

Comparison with Other Pentacene Derivatives

The development of this compound was part of a broader strategy to overcome the limitations of pentacene. The following table compares it with other common derivatives.

| Material | Key Substituent | Solubility & Processability | Stability | OFET Performance (Hole Mobility) |

|---|---|---|---|---|

| Pentacene | None | Insoluble; requires thermal evaporation [3] | Low (sensitive to O₂ and light) [3] [4] | High (up to 5.5 cm²/V·s in thin films) [4] |

| This compound | -Si(CH₂CH₃)₃ | Soluble; enables spin coating and printing [2] | Improved stability against oxygen [3] | ~10⁻⁵ cm²/V·s (highly morphology-dependent) [1] [2] |

| TIPS Pentacene | -Si(CH(CH₃)₂)₃ | Highly soluble; excellent for solution processing [2] | Improved stability against oxygen [3] | Up to 1.8 cm²/V·s (from solution) [2] |

| Soluble Precursors | Reversible adducts | Soluble; converted to pentacene via heat/light [3] | Precursor is stable; converted film shares pentacene's instability | Performance competitive with evaporated pentacene [3] |

Research Significance and Applications

This compound is primarily used in academic and industrial research focused on organic electronics [3]. Its key significance lies in:

- Enabling Solution Processing: It was one of the early demonstrations of how chemical modification could make a high-performance semiconductor soluble, paving the way for low-cost, large-area fabrication techniques like inkjet printing [2].

- Illustrating Structure-Property Relationships: Research on this compound and its cousins (like TIPS pentacene) provides crucial insights into how subtle changes in substituent size and shape can guide crystal packing, which in turn dictates electronic performance [2].

- Application in Prototype Devices: While less performant than TIPS pentacene in thin films, soluble pentacenes as a class have been used to fabricate various prototype devices, including organic thin-film transistors (OTFTs), logic circuits (inverters, NAND/NOR gates), and ring oscillators [2].

References

solubility of triethylsilylethynyl pentacene

Soluble Pentacene Derivatives: A Comparison

The core strategy for making pentacene soluble involves adding bulky silylethynyl groups at the 6 and 13 positions. The table below summarizes key information on two common derivatives.

| Property | TIPS-Pentacene [1] [2] | TMTES-Pentacene [3] |

|---|---|---|

| Full Name | 6,13-Bis(triisopropylsilylethynyl)pentacene | 1,4,8,11-tetramethyl-6,13-triethylsilylethynyl pentacene |

| Chemical Formula | C44H54Si2 | C42H50Si2 |

| Molecular Weight | 639.07 g/mol | 611.017 g/mol |

| Appearance | Dark blue solid [1] | Black crystalline solid [3] |

| Solubility (Qualitative) | Highly soluble in common organic solvents [1] | Soluble in common organic solvents [3] |

| Example Solubility (TIPS, in Toluene) | 6.57 wt. % (~ 66 mg/mL) at 23°C [2] | Information missing |

| Recommended Processing Solvent | Toluene [1] | Toluene [3] |

| Recommended Concentration | 2 mg/mL (for drop casting) [1] | 10 mg/mL (for drop/spin casting) [3] |

| Reported Hole Mobility | >1.0 cm²/V·s [1] | Up to 4.34 cm²/V·s [3] |

Experimental Protocol: Fabricating a TIPS-Pentacene OFET

The following workflow and detailed protocol describe the fabrication of a top-contact, bottom-gate Organic Thin-Film Transistor (OFET) using a drop-casting method [1].

OFET fabrication workflow via drop-casting.

Substrate Preparation

- Cleaning: Sonicate the silicon/silicon dioxide substrates sequentially in a hot 1% Hellmanex III solution, hot deionized (DI) water, and isopropanol (IPA). Rinse with DI water after each step and store in DI water until use [1].

- Surface Treatment: Treat the clean substrates with a silane (e.g., PTES or PTS) to modify the dielectric surface energy. This is crucial for controlling the crystallization of the semiconductor. Immerse the substrates in a 3 mM solution of Trichloro(phenethyl)silane (PTES) in toluene at 90°C for 15 hours in a glovebox [1].

Solution Preparation

- Stock Solution: Dissolve TIPS-Pentacene in anhydrous toluene at a concentration of 10 mg/mL. Stir the solution on a hot plate at 60°C for 1 hour [1].

- Filtration & Dilution: Filter the stock solution through a 0.45 µm filter into a new vial. Dilute the required amount with anhydrous toluene to a final working concentration of 2 mg/mL for drop-casting [1].

Semiconductor Deposition (Drop-Casting)

- Pipette 50 µL of the TIPS-Pentacene working solution (2 mg/mL) onto the prepared substrate [1].

- Place the substrate on a hot plate at 50°C inside a Petri dish, immediately cover with a glass lid to create a solvent-saturated atmosphere, and allow the film to dry for 5 minutes. Switch off the hotplate and let the substrate cool to near room temperature [1].

- The angle of the substrate can be tilted to impose a preferential drying direction, which helps control crystal orientation [1].

Electrode Deposition & Measurement

- Thermal Evaporation: Load the substrates into a thermal evaporator. Pump down to a high vacuum (ca. 2 × 10⁻⁶ mBar) and deposit 80 nm of gold through a shadow mask to define the source and drain electrodes [1].

- Electrical Characterization: Measure the completed OFETs in a probe station under ambient air conditions using a semiconductor parameter analyzer to determine performance metrics like field-effect mobility and threshold voltage [1].

Performance Optimization and Material Blends

For improved device performance and material processability, researchers often blend small-molecule semiconductors like TIPS-Pentacene with polymers.

- Purpose of Polymer Additives: Polymer additives can enhance morphological homogeneity, improve crystal alignment, reduce grain boundaries, and increase device-to-device uniformity [4] [5]. They can also induce vertical phase separation, concentrating the semiconductor at the critical dielectric interface for more efficient charge transport [6] [4].

- Examples of Effective Polymers:

- Poly(α-methyl styrene) (PαMS): An amorphous polymer that, when blended with TIPS-Pentacene at a 50% ratio, has been shown to significantly improve charge carrier mobility and air stability while reducing electrical hysteresis [4].

- Polyisobutylene (PIB): An elastomer that can guide the crystallization of TIPS-Pentacene into densely-arranged, aligned needles, leading to a 3-fold increase in average field-effect mobility and better performance consistency [5].

Finding More Specialized Information

The available data provides a strong foundation for working with soluble pentacenes. To deepen your research:

- Check Manufacturer Datasheets: Suppliers like Ossila and Sigma-Aldrich often provide detailed product information, including solubility, handling procedures, and application notes [3] [2] [1].

- Consult Specialized Literature: For highly specific solubility parameters or the properties of less-common derivatives like TMTES-Pentacene, a focused search on scientific databases using the CAS Numbers (e.g., 373596-08-8 for TIPS-Pentacene) may be necessary.

References

- 1. TIPS-Pentacene [ossila.com]

- 2. 6,13-Bis(triisopropylsilylethynyl)pentacene [sigmaaldrich.com]

- 3. TMTES-Pentacene [ossila.com]

- 4. Study of Comparative Effects of Semicrystalline and ... [sciencedirect.com]

- 5. A facile and novel route to improve TIPS pentacene based ... [sciencedirect.com]

- 6. Microstructural Control of Soluble Acene Crystals for Field- ... [pmc.ncbi.nlm.nih.gov]

Thermal Stability of Acene-Based Semiconductors

The thermal stability of organic semiconductors is a critical factor for device reliability and commercial application. A key challenge is that as the number of fused benzene rings in acenes increases, their stability often decreases [1]. While pentacene derivatives offer high mobility, their stability can be inferior to smaller acenes like tetracene and anthracene [1].

A 2020 study directly investigated the thermal stability of a novel tetracene-anthracene compound, TetAnt. The organic thin-film transistors (OTFTs) based on this material demonstrated high thermal stability, maintaining performance up to 290 °C [1]. This illustrates the stability achievable with acene-based semiconductors.

Stability & Processing of TIPS Pentacene

For the widely used TIPS pentacene, stability and performance are closely tied to fabrication techniques. The table below summarizes key findings:

| Factor | Impact on Stability & Performance | Key Finding / Value |

|---|---|---|

| General Thermal Stability | Operational limit for flexible electronics [2] | Stable on flexible ITO/PET substrates at temperatures enabling flexible electronics |

| Fabrication Temperature | Controls solvent evaporation & crystal formation [3] | Higher substrate temperature improves crystal alignment and charge carrier mobility |

| Polymer Blending (with PαMS) | Prevents thermal cracks from temperature gradient technique [2] | Increases avg. mobility from ~10⁻² cm²/V·s to 0.25 cm²/V·s (on Si) & 0.5 cm²/V·s (on flexible PET) |

Experimental Insights for Assessment

Although a direct protocol for TES pentacene is unavailable, the following methodologies from studies on similar materials provide a framework for evaluation.

1. Thin-Film Transistor (TFT) Fabrication & Testing This is a standard method for evaluating the charge transport properties and stability of organic semiconductors.

- Device Structure: A common configuration uses a heavily doped n-type silicon substrate with a thermally grown silicon dioxide (SiO₂) layer as the gate and gate dielectric, respectively. The organic semiconductor is deposited onto this substrate, followed by the evaporation of source and drain electrodes (e.g., gold) through a shadow mask [2].

- Electrical Characterization: The performance of the TFT, including charge carrier mobility, is typically measured using a semiconductor parameter analyzer under ambient conditions or in a controlled environment [2].

2. Thermal Stability Assessment Protocol A detailed protocol for evaluating thermal stability, as demonstrated for the TetAnt semiconductor, can be adapted [1]:

- Preparation: Fabricate OTFTs based on the material under study.

- Thermal Treatment: Place the finished devices on a hotplate and anneal them in an inert atmosphere (e.g., nitrogen) for a set period.

- In-situ Measurement: Measure the electrical transfer characteristics of the devices in situ at the target temperature.

- Post-treatment Analysis: After annealing, allow the devices to cool to room temperature and remeasure their performance in air to determine any irreversible degradation.

3. Strategy for Enhancing Stability Recent research indicates that electronic modification is a more effective strategy for stabilizing pentacene derivatives than steric protection alone. Specifically, the introduction of electron-withdrawing groups, such as through fluorination, has been shown to enhance the persistence of pentacene derivatives in solution by an order of magnitude [4].

Research Workflow for Thermal Stability Assessment

The diagram below outlines the key stages in a standard workflow for assessing the thermal stability of an organic semiconductor like this compound, based on the methodologies described.

Interpretation and Alternatives

For the most current and direct data, I suggest these pathways:

- Consult Specialized Databases: Search platforms like SciFinder or Reaxys, which are tailored for chemical compound information.

- Review Patent Literature: Technical details are often disclosed in patents before appearing in journal articles.

- Direct Experimental Evaluation: Given the lack of specific data, conducting your own stability tests using the adapted methodologies above may be the most reliable approach.

References

- 1. Thermally stable organic thin film transistors based on 2- ... [sciencedirect.com]

- 2. Temperature gradient controlled crystal growth from TIPS ... [sciencedirect.com]

- 3. Controlling fabrication temperature of TIPS-pentacene to ... [link.springer.com]

- 4. Sterically-Hindered Derivatives of Pentacene and ... [chemrxiv.org]

- 5. Review of the Common Deposition Methods of Thin-Film ... [pmc.ncbi.nlm.nih.gov]

An Introduction to Pentacene-based OFETs

Acene-based molecules like pentacene are a cornerstone of organic electronics due to their highly ordered crystal packing, which favors efficient charge transport [1]. TES Pentacene and TIPS Pentacene are soluble, functionalized derivatives of pentacene designed to overcome the poor solubility of the parent molecule. The trialkylsilylethynyl groups enhance solubility in common organic solvents and improve stability against oxidation, making these materials suitable for solution-processing techniques [1]. OFETs based on these semiconductors are highly relevant for developing flexible, low-cost sensors, displays, and circuits [2].

Material Properties & Preparation

Before fabrication, proper preparation of the semiconductor ink is crucial for reproducible film quality.

Table 1: Semiconductor Ink Formulation

| Component | Specification | Role |

|---|---|---|

| Active Material | TIPS Pentacene | p-type organic semiconductor [3]. |

| Solvent | Toluene | Organic solvent for dissolving the semiconductor [3]. |

| Concentration | 1 mg/mL [3] | Optimal for spin-coating to achieve a ~15 nm thin film [3]. |

OFET Fabrication Workflow

The following diagram outlines the core steps for fabricating a bottom-contact, bottom-gate (BCBG) OFET, a common configuration for research and development.

Diagram 1: Fabrication workflow for a BCBG OFET showing key process stages.

Detailed Experimental Protocols

- Substrate Preparation: Use a heavily doped silicon (n+-Si) wafer with a 200 nm thermally grown silicon dioxide (SiO₂) layer as the gate electrode and dielectric, respectively [3].

- Surface Treatment: Treat the substrate with UV/Ozone for 20 minutes to clean and activate the surface [3]. This step is critical for ensuring effective Self-Assembled Monolayer (SAM) formation.

- Self-Assembled Monolayer (SAM) Application: This step modifies surface energy and reduces charge traps.

- Electrode Treatment: Immerse the substrate in a 0.01 M solution of pentafluorobenzenethiol (PFBT) in toluene for 3 minutes to form a SAM on the gold (Au) source/drain electrodes. This improves charge injection at the metal-organic interface [3].

- Dielectric Treatment: Deposit Hexamethyldisilazane (HMDS) onto the SiO₂ surface, either by spin-coating (4000 RPM, 40 seconds) or exposure to HMDS vapor. This creates a hydrophobic surface that promotes the growth of well-ordered semiconductor crystals [3].

- Semiconductor Deposition:

- Spin-coating: Deposit the TIPS Pentacene solution (1 mg/mL in toluene) onto the prepared substrate and spin at 1000 RPM for 60 seconds in a nitrogen (N₂) environment to prevent oxidation [3].

- Post-processing: Anneal the film as required to remove residual solvent and improve crystallinity.

- Electrical Characterization: Perform electrical measurements in a nitrogen atmosphere to ensure stability. Determine key performance metrics like field-effect mobility (μ) and threshold voltage (Vth) from the saturation regime transfer curve using the standard equation: ( I_D = (W/2L) \mu C_i (V_G - V_{th})^2 ) [3].

Performance Characterization & Optimization

Table 2: Typical OFET Performance for Spin-Coated TIPS Pentacene (BCBG) [3]

| Parameter | Symbol (Unit) | Value |

|---|---|---|

| Charge Carrier Mobility | μ (cm² V⁻¹ s⁻¹) | 0.12 |

| Threshold Voltage | Vth (V) | –1.2 |

| Current On/Off Ratio | I_on/I_off | 10⁵ |

| Device Configuration | - | Bottom-Contact, Bottom-Gate |

Optimization Strategies

The initial performance can be enhanced through several engineering approaches:

- Dielectric Engineering: Using polymer buffer layers like Poly(methyl methacrylate) (PMMA) on electrodes can significantly improve performance. Research shows PMMA can enhance hole mobility by creating a uniform, hydrophobic surface, reducing contact resistance, and favoring semiconductor crystal growth [4].

- Interface Engineering: The SAM treatment process is a form of interface engineering. Optimizing the choice of SAM molecules and deposition parameters can directly reduce charge trapping and improve mobility [2] [5].

- Microstructure Control: The electrical performance is intrinsically linked to the solid-state microstructure and molecular packing of the semiconductor [6]. Techniques like Grazing Incidence Wide-Angle X-ray Scattering (GIWAXS) can be used to characterize the crystallinity and orientation of the semiconductor film, providing insights for further optimization [6].

Application Notes & Troubleshooting

- Environmental Stability: A major challenge for OFETs is operational instability caused by ambient oxygen and moisture [2]. Always perform fabrication and testing in a controlled, inert atmosphere (e.g., N₂ glovebox) where possible.

- Material Substitution: While this protocol is for TIPS Pentacene, the general workflow is applicable to this compound. You will need to empirically optimize parameters such as ink concentration, spin speed, and annealing temperature for the specific material.

- Performance Limitations: Compared to inorganic transistors, OFETs generally exhibit lower charge carrier mobility and operational speed. The values in Table 2 are representative of a solution-processed device, and performance can vary based on specific fabrication conditions [2].

Conclusion

This application note provides a reliable protocol for fabricating and characterizing OFETs using TIPS Pentacene. The provided workflow, from substrate preparation to electrical evaluation, along with the outlined optimization strategies, offers a solid foundation for research into high-performance organic transistors. Researchers can use this guide to develop processes for related semiconductors like this compound.

References

- 1. Reductive Aromatization of 5,7,12,14‐Pentacenetetrone [pmc.ncbi.nlm.nih.gov]

- 2. Organic field-effect transistor-based sensors - RSC Publishing [pubs.rsc.org]

- 3. Fabrication and Evaluation of Organic Field-Effect ... [tcichemicals.com]

- 4. Performance improvement of pentacene organic field-effect ... [scholars.northwestern.edu]

- 5. Performance modification of two-dimensional organic field- ... [sciopen.com]

- 6. In-operando characterizations of oligothiophene OFETs [link.springer.com]

thermal evaporation of TES pentacene thin films

Substance Identification & Hazards

Chemical Identification:

- Product Name: TES pentacene [1]

- CAS Number: 398128-81-9 [1]

- Synonyms: 6,13-Bis((triethylsilyl)ethynyl)pentacene [1]

- Molecular Formula: C₃₈H₄₂Si₂ [1]

- Molecular Weight: 554.91 g/mol [1]

Hazard Identification: this compound requires careful handling. The GHS label includes the signal word "Warning" with the following hazard statements [1]:

- H315: Causes skin irritation

- H319: Causes serious eye irritation

- H335: May cause respiratory irritation

Safety & Handling Protocol

Personal Protective Equipment (PPE) [1]

- Eye/Face Protection: Safety glasses with side-shields conforming to EN166 or equivalent standards (e.g., NIOSH).

- Skin Protection: Wear impervious clothing and gloves. Gloves must be inspected prior to use and disposed of properly after use.

- Respiratory Protection: For nuisance exposures, use a particle respirator (type P95 in US or type P1 in EU). For higher level protection, use type OV/AG/P99 (US) or type ABEK-P2 (EU EN 143) respirator cartridges.

First Aid Measures [1]

- Inhalation: Move person to fresh air. If not breathing, provide artificial respiration and consult a physician.

- Skin Contact: Wash thoroughly with soap and plenty of water. Consult a physician.

- Eye Contact: Rinse cautiously with water for several minutes (at least 15 minutes). Remove contact lenses if present and easy to do. Continue rinsing and consult a physician.

- General Note: Always show the Safety Data Sheet to the attending physician.

Safe Handling and Storage [1]

- Handling: Avoid contact with skin, eyes, and clothing. Avoid dust formation and aerosols. Provide appropriate exhaust ventilation. Handle and store under an inert gas (e.g., Nitrogen, Argon). Protect from light.

- Storage: Keep the container tightly closed in a dry, cool, and well-ventilated place.

Deposition Methods for Pentacene & Derivatives

This compound is a derivative developed to improve the stability and solubility of the original pentacene molecule, primarily to enable solution-processing techniques [2] [3]. The choice of deposition method is fundamental to device performance.

| Deposition Method | Key Principles & Control Parameters | Key Advantages | Key Limitations / Notes |

|---|---|---|---|

| Thermal Vacuum Evaporation [2] [3] [4] | High to ultra-high vacuum (10⁻⁶–10⁻¹² Torr); controlled sublimation; substrate temperature; deposition rate. | High purity films; precise thickness control; well-ordered film structure; good adhesion. | High cost; difficult to scale up; requires high temperatures. The primary method for unmodified pentacene. |

| Organic Vapor-Phase Deposition (OVPD) [3] | Lower vacuum with carrier gas; gas transports evaporated molecules. | Potentially improved large-area uniformity. | Less common than standard thermal evaporation. |

| Solution-Processable Techniques (Spin coating, etc.) [2] [3] | Solvent selection; solution concentration; spin speed; annealing temperature. | Lower cost; suitable for large-scale production; enables flexible electronics. | Enabled by pentacene derivatives like TES-pentacene. |

The experimental workflow for thermal evaporation involves multiple key stages, from substrate preparation to device testing, as illustrated below.

Film Characterization & Performance

Structural and Morphological Characterization:

- Atomic Force Microscopy (AFM): Used to view surface morphology and topology. Pentacene films often exhibit a dendrite structure with sub-micrometer to micrometer grain sizes when deposited on OTS-modified SiO₂, forming a layered structure indicative of a "stand-up" molecular orientation [2] [4].

- X-ray Diffraction (XRD): Used to identify crystallization and phases. Pentacene films can exhibit different phases, such as a thin-film phase (lattice spacing ~15.5 Å) and a bulk phase (lattice spacing ~14.5 Å), which can depend on deposition parameters like time and thickness [2] [5] [6].

- Grazing Incidence X-ray Diffraction (GIXD): Can be used to determine the predominant polymorph in the first few layers of the film, which is crucial for charge transport [7].

Electrical Performance of OTFTs: The table below summarizes the performance of OTFTs based on pentacene and its derivatives, including TES-pentacene, using different deposition methods. Note that the performance for TES-pentacene specifically is limited in the available data [3].

| Material | Deposition Method | Carrier Mobility (cm² V⁻¹ s⁻¹) | Iₒₙ/Iₒff Ratio | Threshold Voltage (V) |

|---|---|---|---|---|

| TES-pentacene | Thermal Vacuum Evaporation | ~10⁻⁵ (Very Low) | NIL (Not In Literature) | NIL [3] |

| Pentacene | Thermal Vacuum Evaporation | 0.18 - 2.5 (Typical) | 10² - 10⁷ | -8.5 to 1.5 [3] |

| TIPS-pentacene | Spin Coating | 0.002 - 3.40 | 10² - 10⁹ | -10 to 3.2 [3] |

| Pentacene/TSB3 | Thermal Evaporation (with interface layer) | Up to 6.3 | >10⁶ | ~ -37.5 [7] |

Application Notes for Researchers

- Material Sensitivity: Pentacene and its derivatives are sensitive to ambient air, specifically oxygen and moisture, which can cause degradation and negatively impact device performance (e.g., reduced mobility, shifted threshold voltage) [2]. Always use an inert atmosphere (glovebox) for storage, handling, and electrical testing [1] [2].

- Interface Engineering is Critical: The substrate surface and any interfacial layers profoundly impact film growth, morphology, and final device performance. Treatments like OTS-SAMs or the use of specific interfacial layers (e.g., TSB3) can dramatically improve crystalline order, reduce grain boundaries, and enhance charge carrier mobility [7] [4].

- Process Control: For reproducible results, meticulously control and document all deposition parameters, including vacuum level, substrate temperature, deposition rate, and final film thickness [4].

- Solution-Processable Alternative: The primary advantage of TES-pentacene and similar derivatives (like TIPS-pentacene) is their solubility, which allows for lower-cost, large-area fabrication techniques such as spin coating and inkjet printing [2] [3].

Important Limitations & Future Work

A significant challenge in preparing these notes is the lack of specific, optimized parameters for the thermal evaporation of TES-pentacene in the available literature. The very low mobility reported for thermally evaporated TES-pentacene suggests it may not be the optimal deposition method for this particular derivative, which was designed for solution processing [3].

Future experimental work should focus on:

- Determining the optimal evaporation temperature and deposition rate for TES-pentacene.

- Systematically investigating the impact of substrate temperature and surface treatments on film morphology.

- Directly comparing the performance and film structure of thermally evaporated versus solution-processed TES-pentacene films.

References

- 1. - Safety TES Sheet pentacene Data [chemicalbook.com]

- 2. Review of the Common Deposition Methods of Thin-Film ... [mdpi.com]

- 3. and Its Derivatives Deposition Methods | Encyclopedia MDPI Pentacene [encyclopedia.pub]

- 4. Performances of Pentacene OFETs Deposited by Arbitrary ... [frontiersin.org]

- 5. Morphological, structural and electrical properties of pentacene thin... [archive.org]

- 6. Morphological, structural and electrical properties of pentacene thin... [beei.org]

- 7. Enhancing 2D growth of organic semiconductor thin films ... [nature.com]

Experimental Protocol: Spin-Coating Pentacene Derivatives

The following workflow and detailed steps are synthesized from methods used for solution-processable pentacene derivatives, primarily TIPS-pentacene [1] [2].

1. Solution Preparation

- Material: Use commercially available TES-pentacene or TIPS-pentacene. For the studies cited here, materials were typically used as received without further purification [1].

- Solvent Selection: Toluene is a common solvent for TIPS-pentacene [3]. Other aromatic solvents like chlorobenzene may also be suitable.

- Concentration: Prepare solutions with a concentration typically in the range of 0.5 to 2 weight percent (wt%) [1] [4]. The optimal concentration depends on the desired final film thickness.

- Mixing: Dissolve the material completely. Note that extended mixing times (e.g., several hours) can lead to molecular aggregation in the solution, which subsequently affects the film's crystalline structure and grain size after deposition [3].

2. Substrate Preparation

- Cleaning: Clean glass or silicon wafer substrates ultrasonically in acetone, ethanol, and isopropanol for about 5 minutes each, followed by oxygen plasma treatment [1].

- Surface Treatment: Apply a self-assembled monolayer (SAM) to modify the dielectric surface. This is critical for improving semiconductor crystallinity and device performance.

3. Spin-Coating Process

- Technique: Deposit the solution onto the prepared substrate and spin-coat.

- Parameters: While specific parameters for TES-pentacene are scarce, one protocol for TIPS-pentacene uses a spin speed of 6000 rpm [1]. The spin time can vary, but shorter times (a few seconds) have been shown to improve molecular order in other organic semiconductors by allowing slower solidification [5].

- Environment: For consistent results, perform the spin-coating in a controlled, inert atmosphere (e.g., a nitrogen glovebox) to prevent degradation from oxygen and moisture [6] [2].

4. Post-Processing (Solvent Vapor Annealing)

- This step is often crucial for achieving high crystallinity in solution-processed small molecules like TES-ADT (a related compound) and TIPS-pentacene [3].

- Place the freshly spin-coated film in a sealed container with a reservoir of a poor solvent, such as 1,2-dichloroethane (DCE) or heptane.

- Expose the film to the solvent vapor for a short period (e.g., 2 to 4 minutes). This exposure allows the molecules to mobilize and form large, interconnected spherulitic crystals, significantly improving charge transport properties [3].

5. Film Characterization After processing, characterize the film quality using standard techniques:

- Structural: Atomic Force Microscopy (AFM) for surface morphology and roughness; 2D Grazing-Incidence X-ray Diffraction (2D-GIXD) for molecular packing and crystalline orientation [6] [3].

- Optical: UV-Vis spectroscopy to analyze absorption and interchain interactions [6] [5].

- Electrical: Fabricate and test Organic Thin-Film Transistors (OTFTs) to measure key electrical performance metrics like charge carrier mobility (μ), on/off ratio (ION/IOFF), and threshold voltage (Vth) [6] [2].

Performance Data and Key Parameters

The table below summarizes electrical performance data for OTFTs based on pentacene and its derivatives from the search results, providing a benchmark for expected outcomes.

| Material | Deposition Method | Carrier Mobility (cm² V⁻¹ s⁻¹) | Iₒₙ/Iₒff | Threshold Voltage (V) | Source |

|---|---|---|---|---|---|

| TES-pentacene | Thermal Evaporation | ~10⁻⁵ | N/L | N/L | [2] |

| TIPS-pentacene | Spin Coating | 0.002 - 1.66 | 10² - 7x10⁹ | -10 to 3.2 | [2] |

| TIPS-pentacene | Shear-Coating | >10 | N/L | N/L | [1] |

| Pentacene | Thermal Evaporation | 0.025 - 2.5 | 10³ - 10⁷ | -8.5 to -1 | [2] |

| Pentacene Precursor (SAP) | Spin Coating | 0.031 | 10³ | -12.5 | [2] |

Key Factors Influencing Performance:

- Grain Boundaries (GBs): In polycrystalline films, GBs act as charge trapping sites, which can degrade field-effect mobility and cause electrical instability under prolonged gate bias (bias-stress instability) [3]. The density of GBs can be influenced by solution preparation, with longer mixing times potentially leading to more nucleation sites and smaller grains [3].

- Solvent Annealing: This step is critical for solution-processed films. It enables the growth of large crystalline domains (spherulites), which reduces the number of detrimental GBs and significantly enhances charge carrier mobility [3].

- Surface Treatment: Modifying the dielectric surface with SAMs or polymer brushes not only improves the initial crystallinity of the semiconductor but can also reduce charge trapping at the critical semiconductor-dielectric interface [1] [3].

Key Recommendations for Protocol Optimization

- Start with TIPS-pentacene Analogies: Given the lack of explicit TES-pentacene data, initial experiments can use established TIPS-pentacene protocols as a baseline. Key parameters to optimize include solution concentration, spin speed, and solvent vapor annealing time and solvent [1] [3].

- Control Crystallization: Since the formation of grain boundaries is a major performance-limiting factor, focus on parameters that control nucleation and crystal growth. Using high-purity solvents, controlling ambient conditions, and optimizing the solvent vapor annealing process are essential [3].

- Prioritize Interface Engineering: The choice of SAM or dielectric surface treatment has a profound impact on device performance. Systematic testing of different surface modifiers is highly recommended [7] [3].

References

- 1. Solution-processed pseudo-vertical organic transistors ... [sciencedirect.com]

- 2. Pentacene and Its Derivatives Deposition Methods [encyclopedia.pub]

- 3. Grain Boundary Induced Bias Instability in Soluble Acene- ... [nature.com]

- 4. Growth of long triisopropylsilylethynyl pentacene (TIPS ... [pubmed.ncbi.nlm.nih.gov]

- 5. Effects of Spin-Coating Time and Processing Additives [nature.com]

- 6. Review of the Common Deposition Methods of Thin-Film ... [pmc.ncbi.nlm.nih.gov]

- 7. Performance improvement mechanisms of pentacene ... [sciencedirect.com]

Comprehensive Application Notes and Protocols for Organic Vapor-Phase Deposition (OVPD) of Pentacene Thin Films

Introduction to Organic Vapor-Phase Deposition (OVPD)

Organic Vapor-Phase Deposition (OVPD) represents an advanced thin-film deposition technique that bridges the gap between laboratory-scale fabrication and industrial production of organic electronic devices. Unlike traditional thermal evaporation methods, OVPD utilizes a carrier gas transport mechanism to deliver organic molecules from a sublimation source to a substrate, enabling precise morphological control and high deposition efficiency. This technology has demonstrated particular promise for depositing pentacene and its derivatives, including triethylsilyl (TES) pentacene, which serve as high-performance organic semiconductors in field-effect transistors, flexible displays, and RF identification tags [1] [2].

The fundamental advantage of OVPD lies in its ability to overcome several limitations associated with conventional vacuum thermal evaporation (VTE). While VTE is limited to deposition rates around 2 Å/s due to poor heat conductivity of organic powders and resulting flux instability, OVPD can achieve deposition rates up to 9.5 Å/s while maintaining excellent film uniformity and electrical characteristics [1] [2]. This enhanced deposition rate, combined with improved thickness uniformity (±3.4% over 30×30 mm²) and reduced material consumption, positions OVPD as a viable technology for roll-to-roll processing of organic electronic devices [2]. Furthermore, OVPD operates at lower vacuum conditions compared to ultra-high vacuum systems, reducing operational costs and complexity while maintaining film purity and performance [1].

Experimental Setup and System Configuration

OVPD Instrument Design

The in-line OVPD system comprises several critical components that work in concert to achieve controlled organic thin-film deposition. As illustrated in Figure 1, the system features a dual-gas line configuration (source and dilution lines) with precision mass flow controllers, a thermally regulated source cell containing the organic material, an elongated showerhead for uniform gas distribution, and a movable susceptor that transports substrates beneath the deposition zone [1]. This configuration enables continuous processing capabilities compatible with sheet-to-sheet and roll-to-roll manufacturing paradigms, significantly enhancing throughput compared to batch-processing systems.

Table 1: Key Components of In-Line OVPD System

| Component | Function | Operational Characteristics |

|---|---|---|

| Source Cell | Sublimes organic material | Temperature-controlled (100-300°C for pentacene) |

| Carrier Gas System | Transports sublimed molecules | Nitrogen, flow rates 50-500 sccm |

| Showerhead Assembly | Distributes gas uniformly | Elongated design for in-line processing |

| Deposition Chamber | Houses substrate and susceptor | Hot-wall, low vacuum operation |

| Susceptor | Positions and moves substrate | Linear motion, temperature control (20-100°C) |

The source cell is strategically positioned within the upper furnace section and is loaded with pentacene powder or its derivatives. Through careful thermal management, the organic material is sublimed into the carrier gas stream without degradation. The hot-wall deposition chamber minimizes temperature gradients and prevents premature condensation of organic species, while the cooled substrate (typically maintained at 20-40°C for pentacene) promotes controlled film formation through surface-mediated condensation [1].

Carrier Gas Dynamics and Flow Optimization

The carrier gas dynamics play a pivotal role in OVPD system performance, directly influencing deposition uniformity, material utilization efficiency, and growth kinetics. Research has demonstrated that the deposition rate profile in an in-line OVPD system follows a predictable distribution pattern, with the highest deposition rates occurring directly beneath the showerhead centerline and gradually decreasing toward the edges [1]. This profile can be mathematically modeled to optimize substrate movement speed and gas flow parameters for maximum thickness uniformity.

Experimental measurements indicate that the carrier gas flow rate linearly correlates with deposition rate, enabling precise control over film growth dynamics. The optimal flow rate range for pentacene deposition typically falls between 100-300 sccm, balancing sufficient molecular flux with proper flow distribution across the substrate surface [1]. The use of nitrogen as carrier gas provides an inert atmosphere that minimizes oxidative degradation of sensitive organic semiconductors during the deposition process, particularly important for pentacene and its derivatives which are susceptible to oxidation [3] [4].

Deposition Parameters and Optimization Protocols

Critical Process Parameters

Successful implementation of OVPD for pentacene thin films requires careful optimization of several interdependent process parameters. These parameters collectively determine the structural morphology, crystallographic orientation, and ultimately the electrical performance of the deposited organic semiconductor films. Based on systematic studies, the most influential parameters include substrate temperature, source temperature, carrier gas flow rate, and system pressure [1].

Table 2: Optimized OVPD Parameters for Pentacene Deposition

| Parameter | Typical Range | Influence on Film Properties | Optimal Value |

|---|---|---|---|

| Substrate Temperature | 20-100°C | Higher temperatures improve ordering but may reduce nucleation density | 40-60°C |

| Source Temperature | 200-300°C | Controls sublimation rate and molecular flux | 250-280°C |

| Carrier Gas Flow | 50-500 sccm | Determines deposition rate and uniformity | 150-250 sccm |

| System Pressure | 0.1-10 Torr | Affects mean free path and deposition kinetics | 1-3 Torr |

| Deposition Rate | 1-10 Å/s | Impacts grain structure and defect density | 5-9.5 Å/s |

The substrate temperature profoundly influences molecular packing and thin-film morphology. For pentacene deposition, temperatures between 40-60°C typically produce the optimal balance between molecular mobility and nucleation density, resulting in films with large, well-ordered crystalline domains essential for high charge carrier mobility [1]. The source temperature must be carefully controlled to maintain a consistent molecular flux without thermal degradation of the organic material, with pentacene typically sublimed at 250-280°C [1].

Deposition Rate Optimization Protocol

Protocol: Optimization of Deposition Rate for Pentacene OVPD

System Preparation

- Load high-purity pentacene powder (≥99.9%) or TES-pentacene derivative into the source cell

- Clean substrate (typically SiO₂/Si with appropriate surface treatments) and mount on susceptor

- Establish system base pressure below 1 Torr and purge with nitrogen

Parameter Initialization

- Set substrate temperature to 40°C

- Initialize carrier gas flow rate to 100 sccm

- Establish source temperature gradient from 200°C to 300°C

Deposition Rate Calibration

- Perform series of short depositions (30-60 seconds) at varying source temperatures

- Measure film thickness by ellipsometry or profilometry

- Construct deposition rate versus source temperature calibration curve

Uniformity Optimization

- Conduct deposition runs across multiple susceptor positions

- Map thickness uniformity using multi-point measurements

- Adjust showerhead configuration and gas flow distribution to achieve ±5% thickness variation

Performance Validation

- Deposit complete thin-film transistors with optimized parameters

- Characterize electrical properties (mobility, threshold voltage, on/off ratio)

- Correlate electrical performance with deposition parameters

This systematic optimization approach has demonstrated the capability to achieve pentacene deposition rates up to 9.5 Å/s with excellent uniformity (±3.4% over 30×30 mm²) and material utilization efficiency of 15% (potentially increasing to 45% with optimized substrate sizing) [2].

Device Performance and Characterization

Electrical Characteristics of OVPD-Fabricated Transistors

Organic thin-film transistors (OTFTs) fabricated using OVPD-deposited pentacene exhibit exceptional electrical performance comparable to devices produced using conventional vacuum thermal evaporation. Research reports hole mobilities of up to 1.35 cm²/V·s with excellent reproducibility across multiple wafers [2]. These devices typically demonstrate high on/off current ratios exceeding 10⁶ and well-behaved output characteristics with clear saturation regions, indicating high-quality semiconductor-dielectric interfaces and minimal contact resistance.

The threshold voltages for OVPD-fabricated pentacene TFTs generally range from -8 to -5 V, with subthreshold slopes that facilitate low-voltage operation—a critical requirement for flexible and portable electronic applications [1] [2]. The consistency of these electrical characteristics across substrate areas demonstrates the superior uniformity achievable with OVPD technology, addressing a significant challenge in scaling organic electronic devices from laboratory to industrial production.

Circuit-Level Implementation and Performance

Beyond individual transistors, OVPD has successfully demonstrated capabilities for complex circuit fabrication using pentacene as the active semiconductor. Five-stage ring oscillators implemented with OVPD-deposited pentacene exhibit oscillation frequencies of 31.4 kHz with a stage delay of 2.7 μs at a supply voltage of 22 V [2]. Additionally, basic logic gates such as AND circuits have been successfully fabricated, operating at supply voltages as low as 10 V while maintaining proper logical functionality.

These circuit-level demonstrations validate OVPD as a viable deposition technology for organic complementary circuits that require consistent semiconductor properties across multiple interconnected devices. The successful implementation of these fundamental circuit building blocks paves the way for more complex organic electronic systems, including display driving circuits, RF identification tags, and sensor interface circuitry [1] [4].

Comparative Analysis with Alternative Deposition Methods

OVPD versus Vacuum Thermal Evaporation (VTE)

When compared with conventional vacuum thermal evaporation, OVPD offers several distinct advantages for industrial-scale organic electronic device fabrication. While VTE is limited to deposition rates around 2 Å/s due to thermal transport limitations in organic powders, OVPD can achieve rates up to 9.5 Å/s without compromising film quality or electrical performance [1] [2]. This enhanced deposition rate directly translates to higher manufacturing throughput and lower production costs.

Additionally, OVPD demonstrates superior material utilization efficiency—approximately 15% compared to typically less than 5% for point-source VTE systems—with potential for further improvement to 45% through optimized substrate sizing and chamber geometry [2]. The use of a carrier gas transport mechanism also enables better thickness uniformity across large-area substrates and reduces particulate contamination through hot-wall chamber design and gas flushing [1].

OVPD versus Solution-Processable Techniques

For pentacene derivatives capable of solution processing (such as TIPS-pentacene), OVPD offers advantages in terms of precise morphological control and reduced sensitivity to solvent compatibility. Solution-based techniques like spin coating and inkjet printing, while offering low equipment costs and high throughput, often struggle with uncontrolled crystallization and poor film uniformity [3] [5]. Additionally, solvent-based processing can introduce compatibility issues with underlying layers and substrates, particularly in multilayer device architectures.

OVPD maintains the high electrical performance associated with vacuum-deposited pentacene (mobilities >1 cm²/V·s) while enabling deposition rates and efficiencies that surpass conventional VTE [2]. This combination of performance and process scalability makes OVPD particularly suitable for applications requiring both high electrical performance and manufacturing viability, such as high-resolution flexible displays and high-frequency RF identification tags [1].

Application Notes and Implementation Guidelines

Substrate Preparation and Surface Treatment

Proper substrate preparation is essential for achieving high-quality pentacene films via OVPD. The substrate surface energy and chemical functionality significantly influence initial nucleation density and subsequent film morphology. For optimal results, SiO₂ dielectric surfaces should receive appropriate surface treatments such as self-assembled monolayers (SAMs) of octadecyltrichlorosilane (OTS) or hexamethyldisilazane (HMDS) to promote two-dimensional growth and enhance molecular ordering [3] [5].

The substrate temperature during deposition should be maintained between 40-60°C for most pentacene derivatives, as this range typically produces the optimal balance between molecular surface mobility and nucleation density. Excessive temperatures may reduce nucleation density and lead to discontinuous films, while insufficient temperatures can result in uncontrolled three-dimensional growth and poor semiconductor performance [1].

Process Optimization for Specific Device Requirements

Different organic electronic applications may require tailored OVPD process conditions to optimize specific device characteristics:

For high-speed circuit applications requiring maximum charge carrier mobility, focus on intermediate deposition rates (5-7 Å/s) and substrate temperatures near 60°C to promote large crystalline domain formation.

For large-area uniform devices such as display backplanes, prioritize thickness uniformity through optimized showerhead design and susceptor movement profiles, potentially accepting slightly reduced mobility for improved reproducibility.

For flexible substrate applications, maintain substrate temperatures below the glass transition temperature of the flexible material (typically <100°C for PET, <150°C for PEN) while adjusting other parameters to compensate for potentially reduced molecular ordering.

The following workflow diagram illustrates the complete OVPD process optimization strategy:

Diagram 1: OVPD Process Optimization Workflow

Troubleshooting Common OVPD Issues

Problem: Poor Film Uniformity

- Potential Causes: Non-uniform gas distribution, temperature gradients across substrate, improper showerhead alignment

- Solutions: Verify showerhead integrity and alignment, improve substrate temperature uniformity, optimize carrier gas flow distribution

Problem: Low Deposition Rate

- Potential Causes: Insufficient source temperature, carrier gas flow rate too low, partial source depletion

- Solutions: Calibrate source temperature, increase carrier gas flow within optimal range, replenish source material

Problem: Defective Film Morphology

- Potential Causes: Substrate temperature outside optimal range, contamination, excessive deposition rate

- Solutions: Adjust substrate temperature, verify system cleanliness and vacuum integrity, reduce deposition rate

Problem: Inconsistent Device Performance

- Potential Causes: Variations in film thickness, changing nucleation behavior, source depletion over time

- Solutions: Implement real-time thickness monitoring, standardize substrate surface preparation, establish source replenishment schedule

Conclusion

Organic Vapor-Phase Deposition represents a viable manufacturing technology for pentacene-based organic electronic devices, effectively bridging the gap between laboratory-scale demonstration and industrial production. The technique offers significant advantages in deposition rate, material utilization efficiency, and thickness uniformity compared to conventional vacuum thermal evaporation, while maintaining the excellent electrical properties associated with pentacene semiconductors. With demonstrated hole mobilities exceeding 1.35 cm²/V·s and successful implementation in functional circuits, OVPD-positioned pentacene devices continue to enable advances in flexible displays, RF identification tags, and other emerging organic electronic applications.

The continued refinement of OVPD process parameters, coupled with developments in pentacene derivative synthesis and purification, promises further enhancements in device performance and manufacturing economics. As the field of organic electronics progresses toward increasingly sophisticated systems and applications, OVPD is poised to play a critical role in the transition from research curiosity to commercial reality.

References

- 1. Growth of pentacene thin films by in-line organic vapor ... [sciencedirect.com]

- 2. (PDF) Pentacene devices and logic gates fabricated by organic vapor... [academia.edu]

- 3. Review of the Common Deposition Methods of Thin-Film ... [pmc.ncbi.nlm.nih.gov]

- 4. Organic passivation layers for pentacene organic thin-film ... [sciencedirect.com]

- 5. and Its Derivatives Deposition Methods | Encyclopedia MDPI Pentacene [encyclopedia.pub]

Comprehensive Application Notes and Protocols: Organic Molecular Beam Deposition (OMBD) of Pentacene Thin Films for Advanced Electronic Applications

Introduction to OMBD and Pentacene Properties

Organic Molecular Beam Deposition (OMBD) represents a highly controlled vacuum deposition technique for producing high-purity crystalline thin films of π-conjugated organic semiconductors like pentacene. This technique enables precise manipulation of molecular orientation and crystalline structure, which are critical parameters determining charge transport properties in organic electronic devices. The ultra-high vacuum (UHV) environment during deposition minimizes contamination and allows for the formation of films with exceptional structural order, making OMBD particularly valuable for fundamental research and high-performance applications. Unlike conventional thermal evaporation, OMBD provides superior control over deposition rates and film morphology, facilitating the growth of highly ordered molecular layers with well-defined interfaces.

Pentacene (C₂₂H₁₄) consists of five linearly fused benzene rings arranged in a planar configuration, creating an extended π-conjugated system that enables efficient charge transport. This molecular structure contributes to its exceptional semiconducting properties, including field-effect mobility values exceeding that of amorphous silicon in optimized devices. However, pentacene exhibits significant challenges in processing due to its low solubility in common organic solvents and susceptibility to degradation when exposed to oxygen and UV light, particularly through the formation of endo-peroxides on the central ring. These limitations make OMBD an ideal deposition technique for pentacene, as it avoids solution processing complications and enables controlled film formation in an inert environment. The crystalline structure of pentacene thin films is particularly complex, with the common existence of multiple polymorphs including the thermodynamically stable single-crystal phase and kinetically favored metastable thin-film phase, which can coexist under specific deposition conditions [1] [2].

Fundamental Principles of OMBD Physics

The OMBD process involves the thermal evaporation of pentacene molecules from a purified source under ultra-high vacuum conditions (typically 10⁻⁶ to 10⁻⁸ Pa), with subsequent ballistic travel to a substrate where they condense and form a thin film. The vacuum environment serves two critical functions: it minimizes contamination from residual gases and creates a mean free path sufficiently long for molecular beam formation without gas-phase collisions. This results in directed molecular flux with well-defined kinetic energy distributions, allowing precise control over the deposition process. The substrate temperature during deposition plays a crucial role in determining molecular mobility upon arrival at the surface, influencing nucleation density, crystalline phase formation, and ultimate film morphology.

The growth mechanics of pentacene during OMBD involve complex intermolecular interactions and molecule-substrate interactions that govern self-assembly. When pentacene molecules arrive at the substrate surface, they undergo surface diffusion until they either nucleate new islands or become incorporated into existing crystalline domains. The molecular orientation in the resulting film is determined by the balance between molecule-substrate interactions and intermolecular interactions. On inert surfaces like SiO₂, pentacene typically adopts a "standing-up" orientation with the molecular plane tilted relative to the substrate surface, optimizing π-orbital overlap for charge transport. However, on graphene templates, the strong π-π interactions between pentacene and the graphene lattice favor a "lying-down" configuration where molecules align parallel to the substrate [3]. This orientation can be manipulated by introducing surface roughness or strain in the graphene template, which destabilizes the lying-down configuration and facilitates a transition to the standing-up orientation that is more favorable for lateral charge transport in devices.

Table 1: Key Deposition Parameters and Their Impact on Pentacene Film Properties in OMBD

| Parameter | Typical Range | Influence on Film Properties | Optimal Values for OTFTs |

|---|---|---|---|

| Deposition Rate | 0.01-0.1 Å/s | Lower rates enhance crystalline order; higher rates promote kinetic phases | 0.01-0.05 Å/s [3] |

| Substrate Temperature | Room temperature to 100°C | Higher temperatures enhance molecular mobility and crystalline size | 55-100°C for mixed phase control [1] |

| Base Pressure | 10⁻⁶ to 10⁻⁸ Pa | Lower pressure reduces contaminants and trap states | <10⁻⁷ Pa [3] |

| Film Thickness | 10-100 nm | Thicker films reduce gate coupling but improve continuity | 30-60 nm [4] |

| Post-deposition Annealing | Room temperature to 100°C | Can improve crystalline order and phase segregation | Substrate-dependent [5] |

Recent Advances in Pentacene OMBD Techniques

Graphene-Templated OMBD

Recent breakthroughs in graphene-templated OMBD have enabled unprecedented control over pentacene molecular orientation. Researchers have discovered that sub-nanometer scale surface roughness and mechanical strain in graphene templates can effectively destabilize the thermodynamically favored lying-down configuration of pentacene molecules. This destabilization facilitates a transition to the standing-up orientation that is particularly advantageous for organic thin-film transistors requiring efficient lateral charge transport. The transition mechanism involves reduced adsorption energy for lying-down pentacene molecules on rough or strained graphene surfaces, while the standing-up configuration remains largely unaffected by these template modifications. This approach represents a significant departure from conventional OMBD on inert substrates and provides a novel strategy for molecular orientation control in organic optoelectronic devices [3].

The graphene-pentacene interface exhibits unique characteristics that differentiate it from conventional substrates. The π-π interactions between pentacene and graphene promote quasi-epitaxial growth with high crystallinity and large grain sizes. Additionally, the clean atomic interface free from dangling bonds improves interface quality in organic/graphene van der Waals heterostructures. Under specific conditions—including controlled surface contamination, graphene-coated rough Cu surfaces, or elevated substrate temperatures during deposition—research groups have observed the formation of energetically unfavorable pentacene thin films with standing-up molecular orientation on graphene templates. These findings suggest that deliberate manipulation of graphene surface properties through strain engineering or roughness control could enable more versatile design of organic optoelectronic devices with optimized charge transport characteristics [3].

Alternative OMBD Approaches

Hyperthermal molecular beam deposition represents a specialized OMBD variant that utilizes supersonic molecular beams to control the kinetic energy of pentacene molecules during deposition. This technique enables the growth of highly ordered thin films at low substrate temperatures (approximately 200 K) when employing kinetic energies of a few electron volts. In contrast, deposition of thermal molecules under identical conditions yields only amorphous films, highlighting the critical role of kinetic energy control in film crystallization. Interestingly, growth at room or higher temperatures produces films of inferior quality irrespective of the depositing beam energy, suggesting complex energy-dependent nucleation mechanisms. The enhanced ordering observed in hyperthermal deposition is interpreted as resulting from local annealing induced by the impact of impinging high-energy molecules, which increases molecular mobility at the deposition site [6].

Neutral Cluster Beam Deposition (NCBD) offers another OMBD variant where neutral cluster beams consisting of weakly bound molecules are produced by evaporated organic molecules undergoing adiabatic expansion in high vacuum. The collision of these unique cluster beams with high translational kinetic energy and directionality against room-temperature substrates induces facile decomposition into individual molecules, with subsequent energetic migration leading to the formation of smooth and uniform thin films. This technique provides the distinct advantage of low-substrate-temperature deposition while maintaining excellent film quality, which cannot be achieved by traditional vapor deposition techniques. The NCBD method has been successfully employed to fabricate organic field-effect transistors and complementary logic gates with improved performance characteristics, demonstrating its viability for organic electronic applications [5].

Experimental Protocols for Pentacene OMBD

Substrate Preparation and Pre-treatment Protocols

Proper substrate preparation is essential for achieving high-quality pentacene thin films with optimal electronic properties. The protocol begins with substrate cleaning using a series of sequential ultrasonic treatments in organic solvents (acetone, isopropanol) followed by oxygen plasma treatment or UV-ozone exposure to remove organic contaminants. For silicon substrates with thermal oxide layers, this cleaning process creates a hydrophilic surface with controlled roughness. Next, surface modification using self-assembled monolayers (SAMs) such as octadecyltrichlorosilane (OTS) or polymer dielectrics like polymethylmethacrylate (PMMA) can be applied to modify surface energy and reduce charge trapping sites. These treatments are particularly important for n-type operation in organic field-effect transistors, as hydroxyl-free dielectrics decrease strong electron traps at the organic semiconductor/dielectric interface [4] [5].

For graphene-templated growth, additional steps are required. CVD-grown graphene is transferred onto the target substrate (typically SiO₂/Si) using standard transfer techniques, followed by thermal annealing under vacuum conditions (300-400°C) to remove polymer residues and contaminants. The quality of the graphene template should be verified using Raman spectroscopy, with characteristic features including a 2D-to-G peak intensity ratio of approximately 2.1 (indicating monolayer graphene) and negligible D peak intensity (confirming low defect density). The surface roughness of the graphene template should be characterized by atomic force microscopy (AFM), with typical values of approximately 0.5 nm for graphene on flat SiO₂. Intentional introduction of surface roughness or strain can be achieved through substrate patterning or transfer onto rough surfaces, providing a mechanism to control pentacene molecular orientation [3].

OMBD System Configuration and Deposition Procedure

A standard OMBD system for pentacene deposition consists of a ultra-high vacuum chamber with a base pressure of 10⁻⁷ to 10⁻⁸ Pa, equipped with multiple Knudsen effusion cells for organic materials, substrate heating stage, thickness monitor, and in-situ characterization capabilities. The following procedure outlines a typical pentacene OMBD process:

Material loading and outgassing: High-purity pentacene powder (sublimation grade ≥99.99%) is loaded into a thoroughly cleaned effusion cell crucible. The system is evacuated to base pressure, and the pentacene source is gradually heated to 100-120°C for 12-24 hours for outgassing to remove volatile impurities.

Substrate mounting and pre-heating: Cleaned substrates are mounted onto the sample holder and transferred into the deposition chamber. The substrates are heated to the desired deposition temperature (room temperature to 100°C) under vacuum for at least 1 hour before deposition to ensure complete desorption of surface contaminants.

Deposition process: The effusion cell temperature is raised to 180-200°C to achieve a stable deposition rate of 0.01-0.05 Å/s, as calibrated by a quartz crystal microbalance. Shutters are opened to begin deposition once the rate stabilizes. Film thickness is typically monitored in real-time, with common thicknesses ranging from 30-60 nm for device applications.

Post-deposition treatment: After deposition, the substrate temperature is maintained for 30-60 minutes to promote further ordering, then gradually cooled to room temperature before breaking vacuum.

Critical parameters requiring careful monitoring throughout the process include deposition rate stability (±5%), substrate temperature uniformity (±1°C), and system pressure during deposition (maintained below 10⁻⁶ Pa). For reproducible results, the same deposition conditions should be maintained across multiple runs, with careful documentation of all parameters [3] [4] [2].

Diagram 1: OMBD Process Workflow illustrating the key stages in pentacene thin film deposition, from substrate preparation to final film characterization.

Characterization Techniques for Pentacene Thin Films

Structural characterization provides essential information about crystalline structure, molecular orientation, and morphology of pentacene thin films deposited via OMBD. Atomic Force Microscopy (AFM) is routinely employed to examine surface morphology, grain structure, and roughness at nanometer-scale resolution. Typical AFM images reveal distinctive island growth patterns, with rod-like islands indicating lying-down molecular orientation and platelet-like islands corresponding to standing-up orientation. The thickness of monolayer islands (approximately 1.5 nm) provides confirmation of molecular orientation, corresponding to a single monolayer of pentacene in a standing-up orientation [3]. X-ray diffraction (XRD) and Two-Dimensional Grazing Incidence X-ray Diffraction (2D-GIXD) are used to determine crystal structure, phase composition, and preferred orientation. These techniques can identify the coexistence of different polymorphs and provide quantitative information about crystalline quality, texture, and lattice parameters [3] [4].

Optical characterization techniques offer insights into electronic structure and molecular organization in pentacene thin films. Ultraviolet-visible spectroscopy (UV-Vis) reveals characteristic absorption spectra that are sensitive to molecular packing and crystallinity. The absorption profile can distinguish between different polymorphic phases and provide information about optical band gaps. Raman spectroscopy provides vibrational fingerprints that are influenced by molecular orientation and intermolecular interactions, making it particularly useful for identifying standing-up versus lying-down configurations on various substrates. Electrical characterization completes the analysis, with organic field-effect transistor (OFET) configurations providing quantitative measurements of charge carrier mobility, threshold voltage, and on/off ratios. Temperature-dependent electrical measurements (20-300 K) can further reveal trapping mechanisms and activation energies for charge transport [3] [4] [5].

Table 2: Characterization Techniques for Pentacene OMBD Films

| Technique | Information Obtained | Typical Results for High-Quality Films |

|---|---|---|

| Atomic Force Microscopy (AFM) | Surface morphology, grain size, roughness | Continuous coverage, terraced islands, roughness < 2 nm |

| X-ray Diffraction (XRD) | Crystal structure, phase composition, orientation | Sharp (00l) reflections for standing-up orientation |

| 2D Grazing Incidence XRD | In-plane and out-of-plane structure, crystallite orientation | Multiple Bragg reflections along qz and qxy directions [3] |

| UV-Vis Spectroscopy | Optical absorption, band gap, molecular aggregation | Distinct vibronic progression, phase-dependent peak positions |

| Raman Spectroscopy | Molecular vibrations, orientation, strain | Characteristic pentacene peaks, orientation-dependent intensity [3] |

| OFET Characterization | Charge carrier mobility, threshold voltage, trap density | Mobility > 0.1 cm²/V·s, on/off ratio > 10⁶ [1] [5] |

Troubleshooting Common OMBD Issues

Poor crystallinity and morphological defects represent frequent challenges in pentacene OMBD. When films exhibit amorphous characteristics or excessively small grain sizes, the primary culprits typically include inadequate substrate temperature, excessive deposition rate, or contamination issues. For improved crystallinity, consider reducing the deposition rate to 0.01-0.02 Å/s to enhance surface diffusion, increasing substrate temperature to 50-70°C (balancing enhanced mobility against possible phase segregation), and verifying source purity through mass spectrometry analysis. Additionally, ensure proper outgassing of both source material and substrate, as adsorbed water and oxygen can significantly disrupt molecular ordering. If using graphene templates, confirm their quality through Raman spectroscopy and optimize the annealing process to remove polymer residues that can interfere with pentacene nucleation [3] [1] [4].

Inconsistent film thickness and uniformity problems often stem from effusion cell instability, improper substrate positioning, or inadequate vacuum conditions. To address these issues, calibrate the quartz crystal microbalance against spectroscopic ellipsometry measurements on reference samples, verify effusion cell temperature stability (±0.1°C) through independent monitoring, and ensure proper collimation and distance between source and substrate. Maintenance of critical vacuum conditions is essential, with base pressure below 10⁻⁷ Pa and minimal pressure rise during deposition. The system should be checked for vacuum leaks and the pumps serviced according to manufacturer recommendations. For orientation control issues specifically on graphene templates, intentional introduction of nanoscale roughness (0.5-1 nm RMS) or strain through substrate engineering can promote the desired standing-up orientation when required for lateral charge transport devices [3] [4].

Diagram 2: OMBD Troubleshooting Guide showing common problems and their solutions for pentacene thin film deposition.

Applications in Organic Electronic Devices

Organic thin-film transistors (OTFTs) represent the primary application for pentacene films deposited via OMBD, with performance parameters strongly dependent on molecular orientation and crystalline quality. The standing-up orientation of pentacene molecules, where the molecular plane is nearly vertical to the substrate surface, provides optimal π-orbital overlap in the direction of charge transport, resulting in higher field-effect mobility. Devices fabricated with optimized OMBD parameters have demonstrated field-effect mobility values exceeding 0.1 cm²/V·s, with some reports reaching 0.38 cm²/V·s for carefully engineered structures. The structural superiority of OMBD-grown films compared to solution-processed alternatives makes them particularly suitable for fundamental charge transport studies and high-performance applications. Additionally, the compatibility of OMBD with patterning techniques enables fabrication of complex integrated circuits, including complementary logic gates such as inverters and NAND gates [1] [2] [5].